# DVB-S2标准高速LDPC编译码器IP核

### 2015.9发布

## LDPC译码器IP特点:

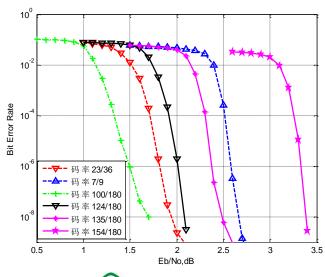

- ✓ 支持DVB-S2标准中定义的21种 LDPC码

- ✓ 支持16200和64800码长

- ✓ 部分并行结构,实现高速处理。ML605开发板(XC6VLX240T芯片)综合最高时钟频率可达192.6MHz

- ✓ 信息数据吞吐率最大可以超过 100Mbps

- ✓ 译码迭代次数可配置,最大迭代次数约为: fclk/fin\*20

- ✓ 主要资源均衡优化,见下表

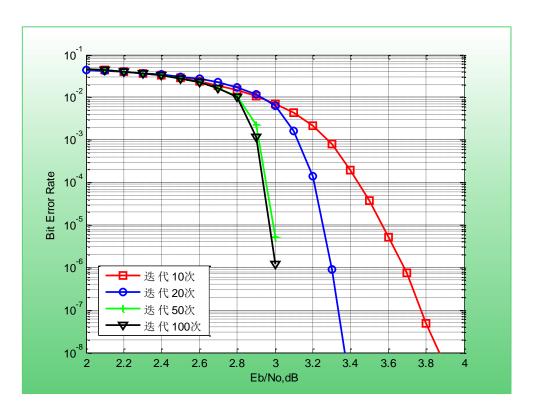

- ✓ 译码算法可配置,支持NMSA、 OMSA等高性能译码算法,下图 中给出的是FPGA下载测试的20次 迭代BER性能曲线

- ✓ 提供完整的MATLAB仿真程序和 testbench测试程序

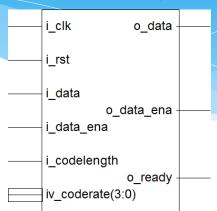

LDPC编码器IP封装管脚说明:

- IN: i clk, 工作时钟

- IN:i rst,全局复位信号

- IN:i data,输入信息位比特

- IN:i data ena, 输入信息位比特使能

- IN: iv coderate, 码率选择

- IN:i codelength,码长选择

- OUT: o data, 输出编码比特

- OUT: o data ena, 输出编码比特使能

- OUT: o ready, 译码完成/允许输入指示

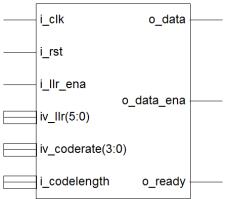

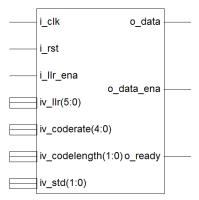

LDPC译码器IP封装管脚说明:

- IN: i clk, 工作时钟

- IN: i rst, 全局复位信号

- IN: i llr ena, 输入对数似然比使能

- IN: iv IIr,输入6比特对数似然比

- IN: iv coderate, 码率选择

- IN:i codelength,码长选择

- OUT: o data、输出译码比特数据

- OUT: o data ena, 输出译码数据使能

- OUT: o ready, 译码完成/允许输入指示

#### 联系方式:

地址:陕西省西安市太白南路2号主楼|区

电话: 029-88203840

# DVB-S2标准高速LDPC编译码器IP核

2015.9发布

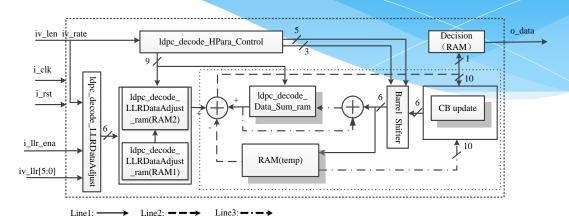

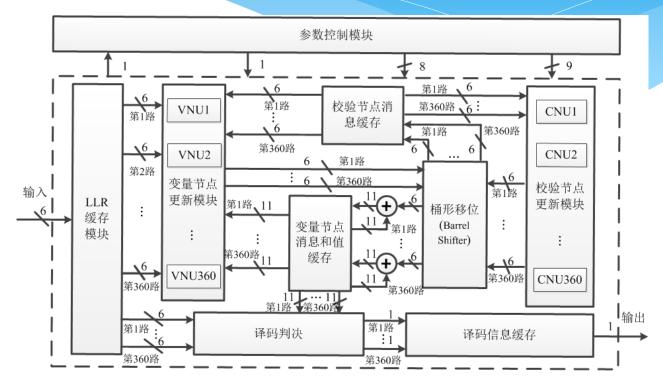

Line2:表示变量节点更新流程,Line3:表示校验节点 更新流程,Line1:表示两种节点更新均进行的流程

| LDPC                    | LDPC编码器IP | LDPC译码器IP           |

|-------------------------|-----------|---------------------|

| Slice Registers         | 1202 (0%) | 21153 ( <b>7%</b> ) |

| Slice LUT               | 3697 (2%) | 37064 (24%)         |

| Block RAM/FIFO          | 83 (19%)  | 174 (41%)           |

| Maximum Frequency (MHz) | 259.7     | 192.6               |

联系方式:

地址: 陕西省西安市太白南路2号主楼|区

电话: 029-88203840

# 兼容DVB-X2/DVB-S2X系列标准的高速 LDPC编译码器IP核

2016.3发布

## LDPC译码器IP特点:

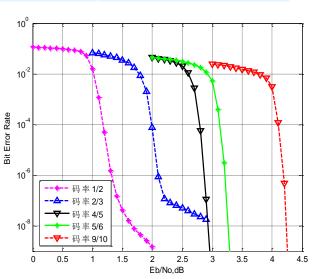

- ✓ 全兼容DVB-S2、DVB-C2、 DVB-T2以及DVB-S2X标准中分 别定义的21、11、13、34种 LDPC码

- ✓ 支持16200、32400、64800码 长

- ✓ 部分并行结构,实现高速处理。 VC707开发板综合最高时钟频率 可达297.3Mbps

- ✓ 信息数据吞吐率最大可以超过 200Mbps

- ✓ 译码迭代次数可配置,最大迭代次数约为: fclk/fin\*40

- ✓ 主要资源均衡优化,见下表

- ✓ 译码算法可配置,支持NMSA、 OMSA等高性能译码算法,下图 中给出的是FPGA下载测试的30次 迭代BER性能曲线

- ✓ 提供完整的MATLAB仿真程序和 testbench测试程序

LDPC编码器IP封装管脚说明:

- IN: i clk, 工作时钟

- IN: i\_rst,全局复位信号

- IN: i\_data\_ena,输入信息位比特使能

- IN: iv\_data, 输入信息位比特

- IN: iv coderate , 码率选择

- IN: iv codelength , 码长选择

- IN: iv std, 2比特标准选择

- OUT: o data, 输出编码比特数据

- OUT: o data ena, 输出编码数据使能

- OUT: o ready,编码完成/允许输入指示

LDPC译码器IP封装管脚说明:

- IN:i clk,工作时钟

- IN:i rst, 全局复位信号

- IN:i llr ena,输入对数似然比使能

- IN: iv IIr,输入6比特对数似然比

- IN: iv coderate, 码率选择

- IN: iv codelength,码长选择

- IN:iv std,2比特标准选择

- OUT: o data,输出译码比特数据

- OUT: o data\_ena,输出译码数据使能

- OUT: o ready,译码完成/允许输入指示

联系方式:

地址: 陕西省西安市太白南路2号主楼|区

电话: 029-88203840

# 兼容DVB-X2/DVB-S2X系列标准的高速 LDPC编译码器IP核

2016.3发布

| LDPC                    | LDPC编码器IP | LDPC译码器IP   |

|-------------------------|-----------|-------------|

| Slice Registers         | 2060 (0%) | 63882 (10%) |

| Slice LUT               | 3395 (1%) | 63540 (20%) |

| Block RAM/FIFO          | 97 (9%)   | 193 (18%)   |

| Maximum Frequency (MHz) | 326.3     | 297.3       |

国家重点实验室

联系方式:

地址:陕西省西安市太白南路2号主楼|区

电话: 029-88203840